BLAST N Overview

BLAST P Overview

SGI RASC Implementation»

Documentation

FAQ

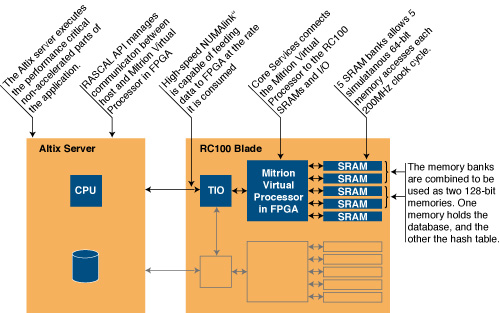

The overall system architecture of the SGI Altix Server with RC100 blades combines high performance CPU processing, high-speed NUMAlink data transfers and large FPGAs with five local memory banks each. In addition, the applications running on the CPU have access to the RASCAL API to configure and communicate with the FPGA. On the FPGA, Core Services connect the Mitrion Virtual Processor (or other computing circuitry) to the RC100 memories and I/Os.

The Mitrion-C accelerated BLAST version relies on the RC100 architecture to provide simultaneous access to multiple SRAM memory banks to stream the nucleotide database through the FPGA and at the same time do continuous hash table look ups. The large Xilinx Virtex-4 FPGA enables extensive parallelization of the parts of the algorithm that are most critical for the performance. The tight integration of the RC100 FPGAs with NUMALink provides the I/O performance needed by the Mitrion Virtual Processor to feed the 1.6 Gbases/s to the algorithm.

Figure 1. Mitrion-C accelerated BLAST and the SGI RC100 system.

| All trademarks are the property of their owners. |